Toshiba

Corporation (TOKYO:6502) ha desarrollado un dispositivo de

protección contra descarga electrostática para la aplicación de

semiconductores de energía analógica. El dispositivo está fabricado con

tecnología de proceso avanzada de 0,13 μm que optimiza la estructura del

transistor y mejora considerablemente las características de ESD

(electrostatic discharge, ESD). La protección contra ESD es mucho más

sólida (hasta cuatro veces más), y la desviación estándar es solo de

1/12 en comparación con la estructura convencional. El análisis de

simulaciones 3D también le ha permitido a Toshiba identificar el

mecanismo para optimizar la estructura del transistor para reforzar la

resistencia a ESD. Toshiba anunció estos avances en el “ISPSD2016”, el

simposio internacional sobre semiconductores que tuvo lugar en República

Checa el 14 de junio de 2016.

Esta edición de Smart News Release (comunicado de prensa inteligente) incluye contenidos multimedia. Vea aquí la publicación completa:

http://www.businesswire.com/news/home/20160615006566/es/

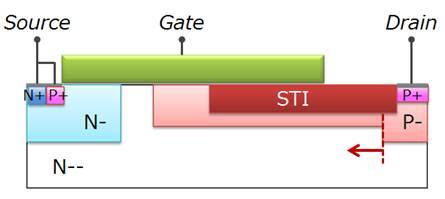

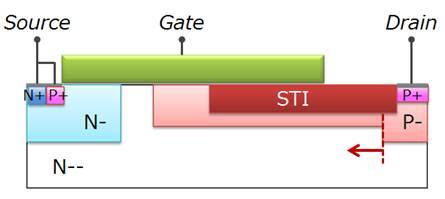

Schematic cross-section of studied structure (Graphic: Business Wire)

Las inyecciones de picos de ESD, ya sea del cuerpo humano o de un

equipo, tienen el potencial de destruir dispositivos semiconductores,

debido a que los flujos de corriente ESD aumentan la temperatura local

de la silicona. Para proteger el circuito interno, se requieren

dispositivos de protección contra ESD. Esto es particularmente

importante en dispositivos semiconductores de energía analógica que

requieren la aplicación de 10V a 100V y necesitan una tensión nominal

alta. En este caso, el dispositivo de protección contra ESD debe

garantizar un alto flujo de corriente, lo cual requiere un chip de mayor

tamaño. La reducción del tamaño del dispositivo de protección contra ESD

es un problema en cuanto a la creación de chips más compactos.

A través del análisis de simulación 3D de un evento de ESD, Toshiba

descubrió que la destrucción inducida por ESD es consecuencia de un

aumento de temperatura en la celosía debido al flujo de corriente en el

punto más alto del campo eléctrico. La modificación de la estructura del

transistor, que consiste en extender la región resistiva baja de drenaje

hasta la dirección de la fuente y suprimir la resistencia de la silicona

lateral, cambia el flujo de corriente de la parte inferior del drenaje

hasta la dirección de la fuente y lo aleja del punto más alto del campo

eléctrico. Este diseño optimizado mejoró la resistencia a ESD hasta

cuatro veces más y disminuyó la desviación estándar a 1/12. Además, el

tamaño del dispositivo requerido para garantizar un HBM* de

±2000V se redujo a 68 %.

Toshiba ofrece plataformas avanzadas de procesos analógicos con

tecnología de proceso de 0,13 μm que pueden combinarse con dispositivos

pasivos, como resistores y condensadores, y transistores bipolares, CMOS

o DMOS. El usuario puede seleccionar el proceso que se adapte a cada

aplicación desde tres plataformas de proceso: El proceso “BiCD-0.13” es

principalmente para el campo automotriz (la línea DMOS es de hasta

100V); el “CD-0.13BL” es principalmente para controladores de motores

(la línea DMOS es de hasta 60V); y el proceso “CD-0.13” es

principalmente para circuitos integrados de administración de energía

(la línea DMOS es de hasta 40V).

Toshiba planea lanzar productos mediante el uso del proceso CD-0.13

aplicado a esta tecnología en 2017 y continuar implementándolo de forma

proactiva a otras plataformas de proceso para mejorar las

características de descarga electrostática.

* Modelo del Cuerpo Humano (Human Body Model, HBM): uno de los

parámetros para indicar la resistencia a ESD

Acerca de Toshiba

Toshiba Corporation, una empresa de la lista Fortune Global 500,

canaliza las capacidades de clase mundial en productos y sistemas

eléctricos y electrónicos avanzados de tres áreas principales de

negocios: Energía que sostiene la vida cotidiana, es más limpia y

más segura; Infrastructura que sostiene la calidad de vida y Almacenamiento

que sostiene a la sociedad de información avanzada. Siguiendo los

principios del Compromiso básico de Toshiba Group, “Comprometidos con la

gente, comprometidos con el futuro” (Committed to People, Committed to

the Future), Toshiba promueve operaciones internacionales y contribuye a

la existencia de un mundo en el que las generaciones futuras vivan mejor.

Fundada en Tokio en 1875, Toshiba, actualmente, se encuentra en el

centro de una red global de 550 empresas consolidadas que emplean a 188

000 personas en todo el mundo, con ventas anuales que superan los 5600

billones de yenes (50 000 millones de USD). (Al 31 de marzo de 2016.)

Para

obtener más información sobre Toshiba, visite www.toshiba.co.jp/index.htm

El texto original en el idioma fuente de este comunicado es la versión

oficial autorizada. Las traducciones solo se suministran como adaptación

y deben cotejarse con el texto en el idioma fuente, que es la única

versión del texto que tendrá un efecto legal.

Vea la versión original en businesswire.com: http://www.businesswire.com/news/home/20160615006566/es/

Hardware

Hardware

Martes 28 de abril - 23:10

Martes 28 de abril - 23:10

Registrar

Registrar  Conectar

Conectar