Toshiba

Corporation (TOKIO:6502) continúa con su compromiso de la promoción

del Internet de las Cosas y el análisis de grandes volúmenes de datos

con el desarrollo de una red neuronal de dominio del tiempo (Time Domain

Neural Network, TDNN)1 que utiliza un circuito semiconductor

neuromórfico de consumo de energía extremadamente bajo a fin de realizar

el procesamiento para el aprendizaje profundo. La TDNN está compuesta de

una cantidad masiva de pequeñas unidades de procesamiento que utilizan

la técnica analógica original de Toshiba, a diferencia de los

procesadores digitales convencionales. La TDNN se presentó el 8 de

noviembre en la A-SSCC de 2016 (Conferencia de Circuitos de Estado

Sólido Asiática de 2016), una conferencia internacional patrocinada por

IEEE sobre la tecnología de circuitos semiconductores celebrada en Japón.

Esta edición de Smart News Release (comunicado de prensa inteligente) incluye contenidos multimedia. Vea aquí la publicación completa:

http://www.businesswire.com/news/home/20161107006737/es/

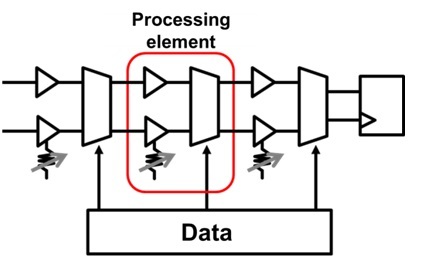

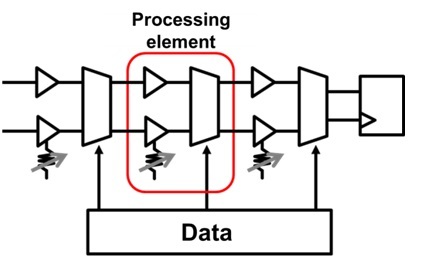

Time Domain Neural Network (Graphic: Business Wire)

El aprendizaje profundo requiere cantidades masivas de cálculos,

generalmente realizados en procesadores de alto rendimiento que consumen

mucha energía. Sin embargo, la integración de la potencia del

aprendizaje profundo a los dispositivos IoT periféricos como sensores y

teléfonos inteligentes, requiere IC de alta eficiencia energética que

puedan realizar las grandes cantidades de operaciones requeridas sobre

un consumo extremadamente bajo de energía.

En la arquitectura de la computadora de tipo von Neumann2, la

mayoría de la energía se consume al mover datos de dispositivos de

memoria con chip interno o externo a la unidad de procesamiento. La

forma más efectiva para reducir el movimiento de un dato es tener

cantidades masivas de unidades de procesamiento, cada una de ellas

dedicada a la manipulación de un solo dato que se encuentre en una

ubicación cercana. A estos puntos de datos se les asigna un peso durante

la conversión de una señal de entrada (p. ej., una imagen de un gato) a

una señal de salida (p. ej., el reconocimiento de dicha imagen como un

gato). Mientras más cerca se encuentre el punto de datos a la salida

deseada, mayor será el peso que se le asigne. El peso provee un

parámetro que guía automáticamente el proceso de aprendizaje profundo.

El cerebro tiene una estructura similar, en el sentido de que la

fortaleza del acoplamiento entre neuronas (dato del peso) se desarrolla

en una sinapsis (unidades de procesamiento). En este caso, las sinapsis

son conexiones entre neuronas y cada una tiene una fortaleza diferente.

Dicha fortaleza (peso) determina la señal que pasa la conexión. De esta

manera, una sinapsis ejecuta un tipo de procesamiento. Esta

arquitectura, que se puede denominar arquitectura desplegada

espacialmente por completo, es atractiva pero tiene una desventaja

obvia: reproducirla en un chip requiere una cantidad masiva de circuitos

aritméticos que se extienden demasiado en poco tiempo.

La TDNN de Toshiba, que emplea técnicas de procesamiento de señales

mixtas analógicas y digitales de dominio temporal (TDAMS)3

desarrolladas en 2013, permite la miniaturización de la unidad de

procesamiento. En las TDAMS, las operaciones aritméticas como la suma se

realizan de manera eficiente mediante el uso del retraso de tiempo del

paso de la señal digital a través de la compuerta lógica como una señal

analógica. Con esta técnica, la unidad de procesamiento para el

aprendizaje profundo puede estar compuesta por solo tres compuertas

lógicas y una memoria de 1 bit con la arquitectura desplegada

espacialmente por completo. Toshiba fabricó un chip de prueba de

concepto que utiliza una célula de SRAM (memoria estática de acceso

aleatorio) como memoria y que ha demostrado el reconocimiento de figuras

manuscritas. El consumo de energía por operación es de 20,6 fJ4,

el cual es 1/6 veces mejor que lo informado con anterioridad en una

conferencia líder5.

Toshiba planea desarrollar la TDNN como una memoria de acceso aleatorio

resistiva (ReRAM) para poder mejorar aún más las eficiencias del área y

la energía. El objetivo es un IC que aplique la tecnología de

aprendizaje profundo en dispositivos periféricos.

-

TDNN: red neuronal que utiliza la técnica de procesamiento de señales

mixtas analógicas y digitales de dominio temporal.

-

Tipo von Neumann: la arquitectura de computadoras estándar más

ampliamente utilizada. La arquitectura carga datos de dispositivos de

memoria a la unidad de procesamiento para el procesamiento.

-

TDAMS: una técnica de procesamiento de señales analógicas que utiliza

el retraso de tiempo del paso de la señal digital a través de la

compuerta lógica como una señal analógica. Desarrollado por Toshiba.

(referencia: http://www.toshiba.co.jp/about/press/2013_02/pr2101.htm)

-

20,6 fJ: Equivalente al desarrollo de 48,6 billones de operaciones en

1 segundo con 1 W de consumo de energía.

-

ISSCC 2016 (Conferencia de Circuitos de Estado Sólido Internacional de

2016), documento número 24.2.

Acerca de Toshiba Corporation

Toshiba Corporation, una

empresa de la lista Fortune Global 500, canaliza las capacidades de

clase mundial en productos y sistemas eléctricos y electrónicos

avanzados de tres áreas principales de negocios: Energía que

sostiene la vida cotidiana, es más limpia y más segura; Infraestructura

que sostiene la calidad de vida y Almacenamiento que sostiene

a la sociedad de información avanzada. Siguiendo los principios del

Compromiso básico de Toshiba Group, “Comprometidos con la gente,

comprometidos con el futuro” (Committed to People, Committed to the

Future), Toshiba promueve operaciones internacionales y contribuye a la

existencia de un mundo en el que las generaciones futuras vivan mejor.

Fundada

en Tokio en 1875, Toshiba, actualmente, se encuentra en el centro de una

red global de más de 550 compañías consolidadas que emplean a más de

188 000 personas a nivel mundial, con ventas anuales que superan los

5600 billones de JPY (50 000 millones de USD). (Al 31 de marzo de 2016).

Para

obtener más información sobre Toshiba, visite www.toshiba.co.jp/index.htm

El texto original en el idioma fuente de este comunicado es la versión

oficial autorizada. Las traducciones solo se suministran como adaptación

y deben cotejarse con el texto en el idioma fuente, que es la única

versión del texto que tendrá un efecto legal.

Vea la versión original en businesswire.com: http://www.businesswire.com/news/home/20161107006737/es/

Hardware

Hardware

Martes 28 de abril - 21:26

Martes 28 de abril - 21:26

Registrar

Registrar  Conectar

Conectar